Summary:

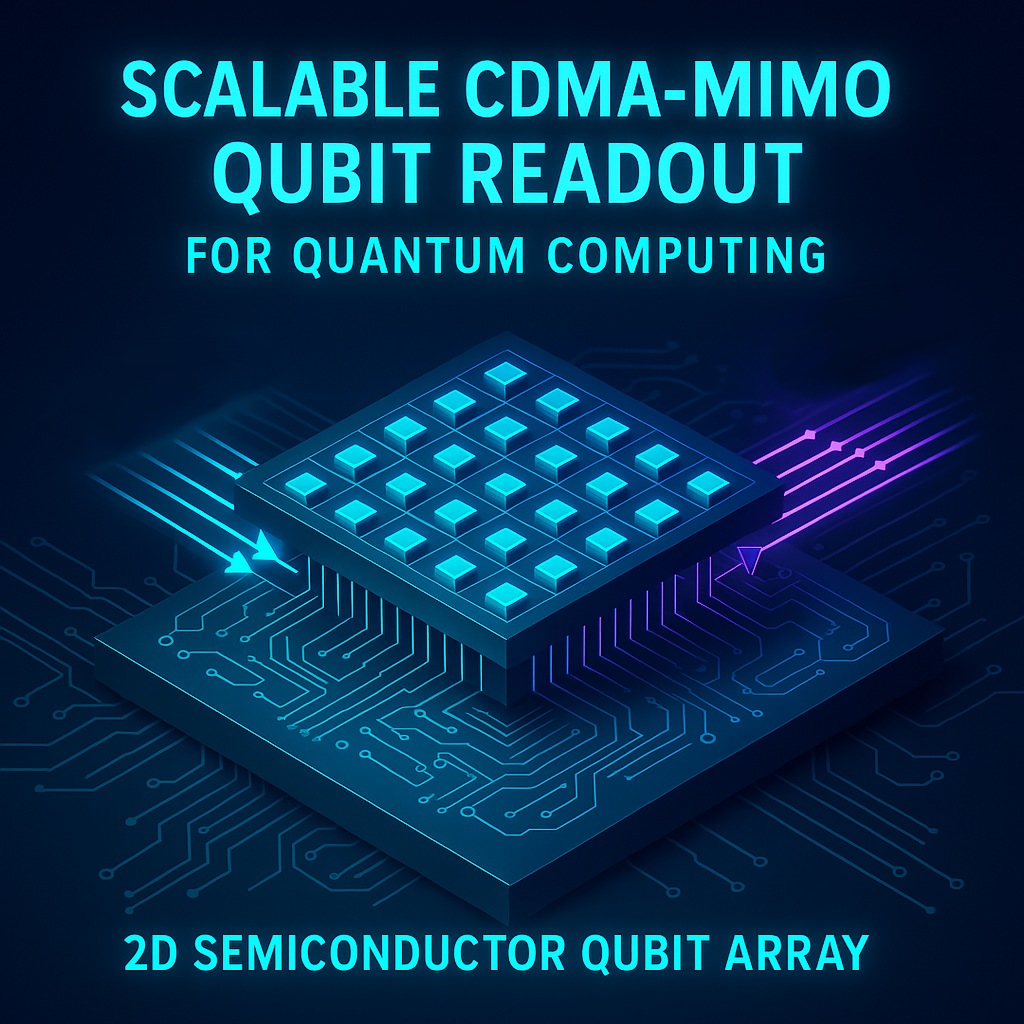

UCLA researchers in the Department of Electrical and Computer Engineering have developed a novel CDMA-MIMO qubit readout network that enables scalable, high-fidelity measurement of two-dimensional semiconductor qubit arrays for fault-tolerant quantum computing.

Background:

Qubit arrays form the foundation of complex quantum computations required in modern quantum processors. Their use enables the key advantages of quantum computing, including high-speed information processing and exponential computational efficiency. A critical step in quantum computing is the process of qubit readout, which involves measuring the final state of each qubit after computation. However, readout is often limited by high error rates and signal interference when many qubits are measured simultaneously. To achieve reliable performance and improve computational output, it is essential to minimize qubit crosstalk and alleviate readout bandwidth bottlenecks. Existing solutions, such as cryogenic CMOS multiplexers, help reduce wiring complexity but can introduce additional electronic noise and consume substantial power at cryogenic temperatures. Improved microwave resonator readout schemes, including Purcell-filtered or frequency-multiplexed designs, enable faster measurements but are hardware-intensive and face scalability limits as qubit counts grow. There remains an unmet need for a scalable, low-power and low cross-talk approach to qubit readout suitable for large semiconductor-based 2D qubit arrays.

Innovation:

Professor Frank Chang and his research team have developed a novel qubit readout network enabling scalable, simultaneous measurement across a two-dimensional semiconductor qubit array. The system combines Code-Division Multiple Access (CDMA) and Multiple-Input Multiple-Output (MIMO) designs to enhance speed, fidelity, and resistance to interference. By multiplexing across both code and spatial domains, the technology supports large-scale readout with lower power demands and strong cryogenic performance. The readouts achieve >99% single-shot fidelity, ensuring accurate, fault tolerant operation. This solution offers a practical pathway toward integrating thousands of qubits on a single chip while maintaining efficient and reliable performance. This innovation significantly advances quantum processor scalability, overcoming key limits of current high-error low-efficiency readout systems.

Potential Applications:

● Semiconductor-based quantum processors

● Large-scale 2D qubit arrays

● Fault-tolerant quantum computing systems

● Quantum simulators for complex physical systems

Advantages:

● Low power consumption at scale

● High single-shot readout fidelity (>99%)

● Scalable for large qubit arrays

● Robust performance at cryogenic temperatures

Development Status:

First description of complete invention Nov. 16, 2024

Reference:

UCLA Case No. 2025-153

Lead Inventor:

Professor Mau-Chung Frank Chang, Department of Electrical and Computer Engineering